De visie voor toekomstige processors met bijna het dubbele van de transistordichtheid begint vorm te krijgen, nu alle drie de grote chipfabrikanten CFETS of Complementary Field Effect Transistors hebben gedemonstreerd. CFET’s zijn een enkele structuur die beide typen transistors combineert die nodig zijn voor CMOS-logica. Op de IEEE International Electron Devices Meeting deze week in San Francisco lieten Intel, Samsung en TSMC de vooruitgang zien die ze hebben geboekt in de richting van de volgende evolutie van transistors.

Chipbedrijven stappen over van de FinFET-apparaatstructuur die sinds 2011 wordt gebruikt naar nanosheets, of all-access-transistors. De namen weerspiegelen de basisstructuur van de transistor. Bij een FinFET regelt de poort de stroomstroom door de verticale siliciumvin. In een nanosheet-apparaat wordt die vin in een reeks stroken gesneden, elk omgeven door een poort. Een CFET neemt in wezen een hogere stapel strips in beslag en gebruikt de helft voor het ene apparaat en de andere helft voor het andere. Dit apparaat, zoals Intel-ingenieurs hebben uitgelegd in het nummer van december 2022 IEEE-spectrumbouwt twee typen transistors – nFET en pFET – op elkaar in één geïntegreerd proces.

Deskundigen schatten dat CFET’s over zeven tot tien jaar commercieel zullen worden geïntroduceerd, maar er moet nog veel werk worden verzet voordat ze klaar zijn.

Intel-omvormer

Intel was de eerste van de drie die de CFET demonstreerde en in 2020 op de IEDM een vroege versie onthulde. Deze keer rapporteerde Intel verschillende verbeteringen rond het eenvoudigste circuit dat de CFET maakt, de converter. Een CMOS-omvormer stuurt dezelfde ingangsspanning naar de poorten van beide apparaten in de stapel en produceert een uitvoer die het logische omgekeerde is van de invoer.

“De omvormer is gemaakt op één pen”, vertelde Marko Radosavljević, hoofdingenieur van Intel’s componentenonderzoeksgroep, vóór de conferentie aan verslaggevers. “Bij maximale schaalvergroting zou het 50 procent” zijn van de grootte van een gewone CMOS-converter, zei hij.

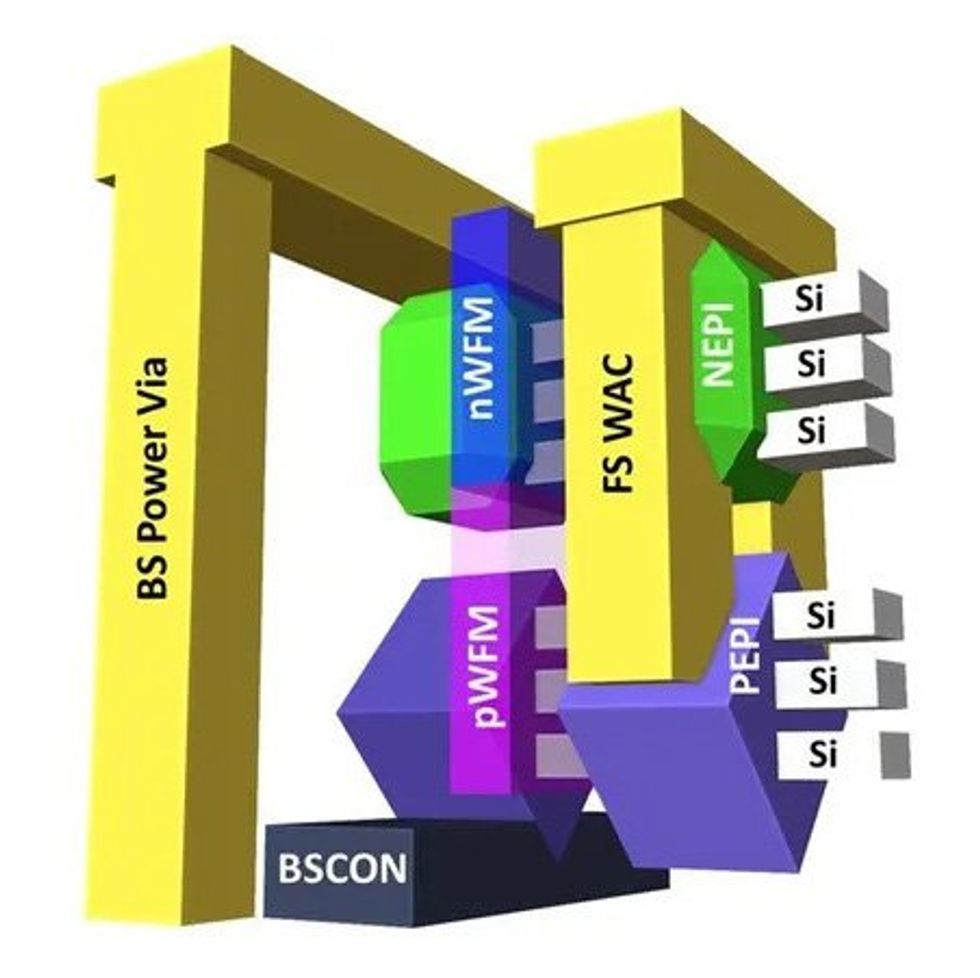

De invertercircuits van Intel zijn afhankelijk van een nieuwe manier om de bovenste en onderste transistors met elkaar te verbinden [yellow] en in contact met een van hen onder het silicium [grey]Intel

De invertercircuits van Intel zijn afhankelijk van een nieuwe manier om de bovenste en onderste transistors met elkaar te verbinden [yellow] en in contact met een van hen onder het silicium [grey]Intel

Het probleem is dat het samenpersen van alle verbindingen die nodig zijn om die twee transistors in een invertercircuit te veranderen, het gebiedsvoordeel opslokt. Om de zaken solide te houden, heeft Intel geprobeerd een deel van de congestie weg te nemen die gepaard gaat met het verbinden met een gestapeld apparaat. Bij de huidige transistors komen alle verbindingen van de bovenkant van het apparaat zelf. Maar later dit jaar implementeert Intel een technologie genaamd backside power supply, waarmee verbindingen zowel boven als onder het siliciumoppervlak kunnen bestaan. Door die technologie te gebruiken om vanaf de onderkant contact te maken met de onderste transistor in plaats van vanaf de bovenkant, werd het circuit aanzienlijk vereenvoudigd. De resulterende omzetter had een dichtheidskwaliteit die contactpolypitch (CPP, in wezen de minimale afstand van de ene transistorpoort naar de andere) wordt genoemd, van 60 nanometer. De huidige 5 nm-knooppuntchips hebben een CPP van ongeveer 50 nm.

Bovendien verbeterde Intel de elektrische eigenschappen van de CFET-stack door het aantal nanosheets per apparaat te verhogen van twee naar drie, de afstand tussen twee apparaten te verkleinen van 50 nm naar 30 nm, en een verbeterde geometrie te gebruiken om de apparaatonderdelen met elkaar te verbinden.

De geheime saus van Samsung

Samsung ging zelfs kleiner dan Intel en liet resultaten zien voor 48 nm en 45 nm contact polypitch (CPP), vergeleken met Intel’s 60 nm, hoewel deze voor individuele apparaten waren en niet voor complete converters. Hoewel er enige prestatievermindering was bij de kleinere van de twee CFET-prototypes van Samsung, was dat niet veel, en de onderzoekers van het bedrijf geloven dat optimalisatie van het productieproces daarvoor zal zorgen.

Cruciaal voor het succes van Samsung was de mogelijkheid om de source en drain van gestapelde pFET- en nFET-apparaten elektrisch te isoleren. Zonder voldoende isolatie zal het apparaat, dat Samsung een 3D gestapelde FET (3DSFET) noemt, stroom lekken. Een belangrijke stap in de richting van het bereiken van die isolatie was het vervangen van een etsstap waarbij natte chemicaliën betrokken waren, door een nieuw type droog etsen. Dit leidde tot een stijging van 80 procent in de opbrengst van goede apparaten.

Net als Intel heeft Samsung contact gemaakt met de onderkant van het toestel onder het silicium om ruimte te besparen. De Koreaanse chipmaker verschilde echter van de Amerikaanse door in elk van de gekoppelde apparaten één nanosheet te gebruiken in plaats van de drie van Intel. Volgens zijn onderzoekers zal het vergroten van het aantal nanosheets de CFET-prestaties verbeteren.

TSMC geeft zijn kans

Net als Samsung wist ook TSMC de industrieel relevante stap van 48 nm te bereiken. Kenmerken van zijn apparaat omvatten een nieuwe manier om een diëlektrische laag tussen de bovenste en onderste apparaten te vormen om ze te isoleren. Nanosheets worden over het algemeen gevormd uit afwisselende lagen silicium en siliciumgermanium. In een geschikte stap in het proces verwijdert een silicium-germanium-specifieke etsmethode dat materiaal, waardoor de silicium nanodraden vrijkomen. Voor de laag die bedoeld was om de twee apparaten van elkaar te isoleren, gebruikte TSMC siliciumgermanium met een ongewoon hoog aandeel germanium, wetende dat het sneller zou etsen dan andere SiGe-lagen. Op deze manier kon de isolatielaag in verschillende stappen worden opgebouwd voordat de silicium nanodraden loskwamen.

Uit artikelen op uw website

Gerelateerde artikelen op internet