In de afgelopen vijf jaar isIntel bleef achter bij Taiwan Semiconductor Manufacturing Co. en Samsung in geavanceerde chipproductie. In een poging de leiding terug te winnen, maakt het bedrijf nu een gedurfde (en riskante) stap door twee nieuwe technologieën te introduceren in zijn desktop- en laptop Arrow Lake-processor, die eind 2024 op de markt komt. Intel hoopt zijn concurrenten een voorsprong te geven met een nieuwe transistortechnologie en een systeem voor energielevering, dat de eerste in zijn soort zou zijn.

De afgelopen twintig jaar heeft Intel het voortouw genomen bij het introduceren van belangrijke veranderingen in de transistorarchitectuur, zegt Chris Auth, Intel’s vice-president van technologieontwikkeling en directeur van geavanceerde transistorontwikkeling. De chipproductie van het bedrijf heeft echter een meer bewogen verleden achter de rug: in 2018 was Intel niet in staat zijn eerste 10-nanometer CPU op tijd te leveren, en werd de chipproductie met een jaar uitgesteld, waardoor er een tekort ontstond aan CPU’s gemaakt met behulp van zijn 14-nanometer CPU’s. nanometer-processors. nm-technologie. In 2020 was er opnieuw vertraging, dit keer voor het 7nm-knooppunt (omgedoopt tot Intel 4). Sindsdien is het bedrijf bezig met een inhaalslag.

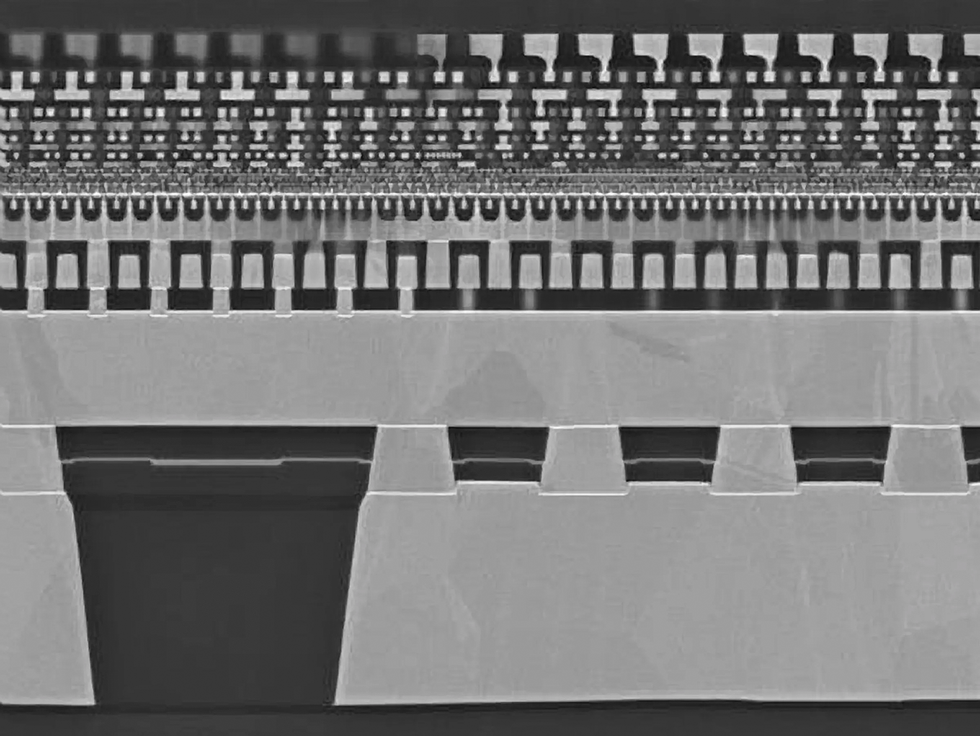

RibbonFET, de nanosheet-transistor van Intel, zal de huidige FinFET-technologie vervangen. FinFET-transistoren maakten processors mogelijk met lage stroomvereisten en een hogere logische circuitdichtheid door de poort van de transistor aan drie zijden rond het kanaalgebied te wikkelen in plaats van slechts één. Maar nu FinFET’s kleiner zijn geworden, hebben deze apparaten de grens bereikt van het vermogen van hun poorten om de stroom te controleren. Nanosheet-transistoren, zoals de Multi-Bridge-Channel FET van Samsung, bieden betere controle omdat hun poort het kanaalgebied volledig omringt. Intel verwacht een verbetering van de energie-efficiëntie tot 15 procent met RibbonFET wanneer het wordt geïntroduceerd in de komende Intel 20A-processornode – de nieuwste halfgeleiderproductieprocestechnologie van het bedrijf. De “A” in 20A verwijst naar Angstrom, hoewel deze, net als de “nanometer” in de vorige naamgevingsconventie voor chips, niet langer verwijst naar een specifieke meting in een product.

De introductie van een nieuw stroomafgifteschema – doorgaans back-side power genoemd en dat Intel PowerVia noemt – is een dramatischere verandering. “Sinds Robert Noyce het eerste geïntegreerde circuit bouwde, speelde alles zich af op het gebied van de interconnectie”, zegt Auth. Dit zal de eerste keer zijn dat fabrikanten ook het oppervlak aan de andere kant van de wafer zullen gebruiken, waardoor kracht en verwerking worden gescheiden. Die scheiding is belangrijk omdat hoogspanningslijnen en signaallijnen verschillende optimalisaties hebben: terwijl hoogspanningslijnen het beste werken met draden met lage weerstand en hoge dikte, hebben signaallijnen meer ruimte ertussen nodig om minimale interferentie te garanderen.

“Het is een soort nieuwe speeltuin”, zegt Julien Ryckaert, vice-president Logic Technologies bij Imec. De overstap naar nanosheettechnologie is conventioneel, maar Ryckaert ziet kansen voor innovatieve nieuwe functies met kopkracht.

Twee technologieën tegelijk

Intel besloot ongeveer vijf jaar geleden beide technologieën tegelijkertijd te introduceren, rond dezelfde tijd dat het zijn voorsprong op de concurrentie verloor. Normaal gesproken lopen dit soort projecten over een tijdlijn van tien jaar. Naarmate Intel dichter bij de implementatie van het nieuwe transistor- en energieleveringsnetwerk kwam, zagen de leidinggevenden deze tijdlijnen elkaar kruisen. Daarom besloot het bedrijf deze technologieën te koppelen, om de concurrentie voor te blijven en te voorkomen dat je moest wachten tot het volgende knooppunt de een of de ander introduceerde. Beide worden gezien als ‘cruciale schakels’ voor Intel’s ambitieuze doel om tegen 2025 het leiderschap op het gebied van verwerkingstechnologie terug te winnen, zegt Auth.

“Intel was vroeger conservatief”, zegt Dan Hutcheson, vice-president van TechInsights. Voorheen was TSMC agressiever in het nemen van risico’s en miste het bedrijf vaker het doel. Nu is de situatie omgekeerd, legt Hutcheson uit. “Het is een zeer riskante zet om twee grote technologische veranderingen tegelijk door te voeren, en in het verleden was het vaak een recept voor rampen”, zegt hij.

Intel’s innovatie moet gepaard gaan met een betrouwbare productie om klanten aan te trekken en te behouden, voegt Hutcheson toe, vooral omdat het bedrijf zijn activiteiten blijft verschuiven naar een halfgeleidergieterijmodel door zijn productie- en productgroepen te scheiden. In het gieterijmodel is het belangrijk dat klanten de fabrikant kunnen vertrouwen, zegt hij. Vanwege de langetermijninvestering vanaf de ontwikkeling tot de levering van het product, wedden klanten “zo’n twee jaar later in wezen op de boerderij.”

De leidinggevenden van het bedrijf zijn zich bewust van de risico’s die zij nemen, gezien de tegenslagen en vertragingen waarmee Intel te maken heeft gehad met het 10-nm-knooppunt. Hoewel de sector ‘gebouwd is op het nemen van risico’s’, zegt Auth, ‘was dit een geval waarin we te veel risico namen en we zijn ons zeker bewust van die fout.

Om het risico dat gepaard gaat met het komende 20A-knooppunt te verminderen, heeft Intel een intern knooppunt toegevoegd dat PowerVia koppelt aan de huidige generatie FinFET’s. Volgens testresultaten die in juni 2023 werden gepresenteerd, leidde de toevoeging van PowerVia alleen al tot een prestatieverbetering van 6 procent. Dankzij deze interne springplank kon het bedrijf de vermogensafgifte vanaf de achterkant testen en eventuele problemen oplossen, zowel qua proces als qua ontwerp.

Qua proces moet Intel bijvoorbeeld uitzoeken hoe de voor- en achterkant van de chip op de juiste manier kunnen worden uitgelijnd en verbonden met verticale connectoren van nanometerformaat, silicium vias genaamd, die 1/500 van de grootte van eerdere connectoren zijn. Een andere uitdaging is het handhaven van de vlakke oppervlakken die nodig zijn om de chips te vormen wanneer aan beide zijden van de siliciumwafel wordt gewerkt, zegt Auth.

Gezien deze behoefte aan een nog grotere productieprecisie zijn de verwachte kosten het overwegen waard, zegt Mark Horowitz, hoogleraar elektrotechniek aan de Stanford University. Historisch gezien is de prijs per transistor gedaald omdat fabrikanten zijn overgestapt op betere technologieën. Nu zijn deze kostenverbeteringen over het algemeen stabiel gebleven. “Transistors worden niet zo snel goedkoper als vroeger”, zegt Horowitz.

Ondertussen moeten ontwerpers de verbindingslijnen en lay-out heroverwegen. Door met PowerVia elektrische kabels naar de achterkant van de chip te verplaatsen, zegt Auth, “maak je ongeveer zeven jaar kennis over interconnecties aan de voorkant ongedaan.” Ingenieurs moesten bijvoorbeeld opnieuw leren hoe ze gebreken konden opsporen en warmte op de juiste manier konden afvoeren. Ondanks de steile leercurve verwacht Intel aanzienlijke voordelen uit de combinatie van nieuwe technologieën.

Nu elke vooruitgang het onafhankelijke aspect van schaalvergroting aanpakt, kan het nieuwe transistor- en stroomleveringsnetwerk als complementair worden beschouwd, aldus Ryckaert van Imec. Hij vermoedt dat Intel’s beslissing om backplane-stroom te introduceren tijdens de overgang van FinFET naar nanosheets werd genomen om klanten aan te trekken, wat een groter voordeel opleverde dan beide vooruitgangen op zichzelf zouden kunnen opleveren. Er zijn misschien niet veel toekomstige generaties die nanosheet-transistortechnologie gebruiken. “We zullen heel snel een verzadiging van nanosheets zien”, voorspelt Ryckaert.

Intel verwacht in de eerste helft van 2024 klaar te zijn om de 20A te produceren. TSMC is van plan begin 2025 te beginnen met de productie van chips met zijn N2-nanosheettechnologie. De productie van N2P-chips – de versie met voeding aan de achterkant – zal naar verwachting in 2026 beginnen. Samsung heeft in 2022 al nanosheet-transistoren geïntroduceerd in zijn 3-nm-node, maar heeft nog niet officieel een tijdlijn voor back-end-implementatie aangekondigd.

Hutcheson is van mening dat alle chipmakers zich op dezelfde weg naar herstel bevinden; Intel is pas de eerste die de stap zet. Als het bedrijf daarin slaagt, kan het door dat risico zijn voorsprong herwinnen, zegt hij. “Hier komt veel bij kijken.”

Dit artikel verschijnt in de gedrukte editie van januari 2024 als “Intel hoopt zijn rivalen een sprong voorwaarts te maken”.

Uit artikelen op uw website

Gerelateerde artikelen op internet