Er zijn veel beperkingen bij het ontwerp van augmented reality-systemen. Niet in de laatste plaats is dat “je er representatief uit moet zien als je rondloopt”, vertelde Meta-onderzoeker Tony Wu dinsdag aan ingenieurs op de IEEE International Solid State Circuits Conference (ISSCC). “Je kunt niet de hele tijd een schoenendoos op je gezicht hebben.”

Het AR-systeem moet ook licht van gewicht zijn en niet veel warmte kunnen afgeven. En het moet bescheiden zijn qua vermogen, want niemand wil draagbare elektronica om de paar uur opladen. Aan de andere kant, als je een gloeiende schoenendoos op je gezicht hebt, ben je misschien dankbaar voor de korte batterijduur.

De 3D-chip kan twee handen tegelijkertijd volgen en verbruikt 40 procent minder energie dan een kubus met slechts één hand. Bovendien deed hij het 40 procent sneller.

Wu maakt deel uit van het Meta-team dat werkt aan een slim siliciumapparaat om een AR-systeem te maken, genaamd Aria, dat zo groot is als ze maar kunnen maken. Een groot deel van de oplossing, zo vertelde Wu aan de ingenieurs, is 3D-chipintegratietechnologie. Bij ISSCC legde Meta uit hoe de prototype AR-processor van het bedrijf 3D gebruikt om meer te doen in hetzelfde gebied met dezelfde hoeveelheid of minder kracht.

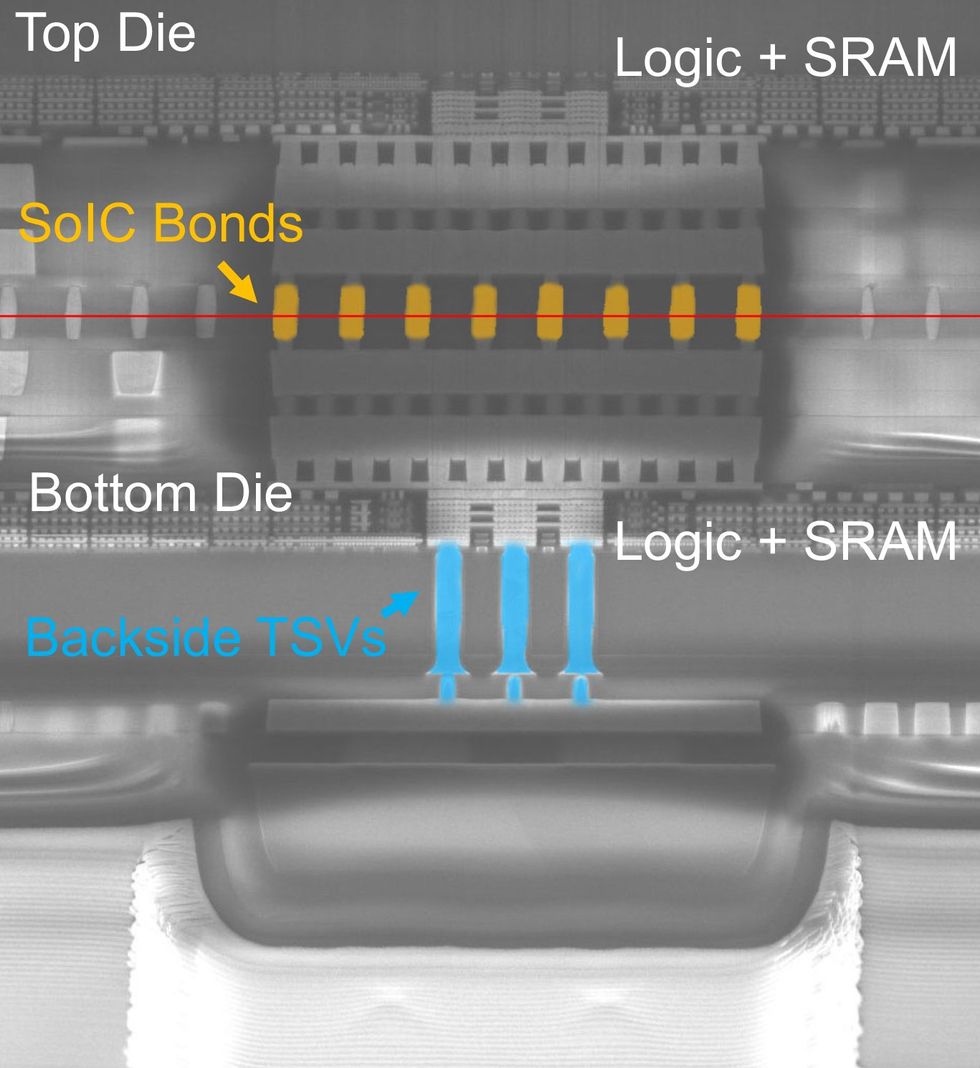

Meta’s prototypechip heeft zowel logica als geheugen op elke siliciumwafel. Ze zijn face-to-face met elkaar verbonden en verzenden gegevens en stroom voor beide via een siliciumverbinding (TSV).Doel

Meta’s prototypechip heeft zowel logica als geheugen op elke siliciumwafel. Ze zijn face-to-face met elkaar verbonden en verzenden gegevens en stroom voor beide via een siliciumverbinding (TSV).Doel

De prototypechip bestaat uit twee IC’s van gelijke grootte: 4,1 x 3,7 millimeter. Ze zijn met elkaar verbonden in een proces dat face-to-face wafer-to-wafer hybride binding wordt genoemd. Zoals de naam al aangeeft, houdt het in dat twee volledig bewerkte wafers naar elkaar toe worden gedraaid en met elkaar worden verbonden, zodat hun onderlinge verbindingen rechtstreeks met elkaar zijn verbonden. (Het “hybride verbindings”-gedeelte betekent dat het een directe koper-op-koperverbinding is. Solderen is niet nodig.)

De TSMC-technologie die hiervoor werd gebruikt, zorgde ervoor dat ongeveer elke 2 micrometer twee stukjes silicium een verticale verbinding konden vormen. Het prototype maakte niet optimaal gebruik van deze dichtheid: er waren ongeveer 33.000 signaalverbindingen tussen twee stukken silicium en 6 miljoen stroomverbindingen nodig. De onderste chip maakt gebruik van siliciumvia’s (verticale verbindingen die door het silicium zijn geponst) om signalen uit de chip te trekken.

Dankzij de 3D-stapeling kon het team de rekenkracht van de chip vergroten, waardoor deze grotere taken kon uitvoeren, zonder de omvang ervan te vergroten. De machine learning-eenheid van de chip heeft vier rekenkernen op het onderste bord en 1 megabyte lokaal geheugen, maar de bovenste chip voegt daar nog eens 3 MB aan toe, beschikbaar via 27.000 verticale datakanalen met dezelfde snelheid en energie (0,15 picojoule/byte) alsof ze dat waren. één groot stuk silicium.

Het team testte de chip op een machine learning-taak die cruciaal is voor augmented reality, handtracking. De 3D-chip kon twee handen tegelijkertijd volgen en gebruikte 40 procent minder energie dan een kubus met slechts één hand. Bovendien deed hij het 40 procent sneller.

Naast machine learning kan de chip beeldverwerkingstaken uitvoeren. 3D maakte hier opnieuw een groot verschil. Terwijl de 2D-versie beperkt was tot gecomprimeerde beelden, kan de 3D-chip full HD doen met hetzelfde vermogen.

Uit artikelen op uw website

Gerelateerde artikelen op internet